2007/10/18 15:02

建立布林代數式剛才說《表二》是以橫向一列一列的建立起來,但是建立布林代數式時,則要以縱向一行一行的看表二。為什麼?因為現在我們要以每個LED為考量,看看每個LED在什麼條件下發光,以表二LED B為例,垂直看下來,0比1多那麼我們就以1來說明比較簡單。當LED B要熄滅時 (B=1) 的條件為:

當SEL為0且CLK為0且F2~F0 =3或SEL為0且CLK為0且F2~F0=7或SEL為0且CLK為1且F2~F0=3或SEL為0且CLK為1且F2~F0=7或SEL為1且CLK為0且F2~F0=7或SEL 為1且CLK 為1且F2~F0=7的時候LED B會熄滅﹝即B=1﹞。

以上冗長的描述就已經是布林代數式的骨架,只要稍加修改即可:

其中SEL等信號上方加上一直線代表該函數值為0,沒加代表該函數值為1,“‧”代表AND運算,“+” 代表OR運算;這就是LED B的布林代數式。依此方式即可將其他LED的布林代數式列出。再回頭看表二LED A這一行,剛才沒有先舉LED A為例是因為這行太特殊了,仔細一看全部是零!這下布林代數式怎麼寫呢?很簡單,就是:A = 0, 也就是說A不管任何輸入條件,只要一開機就是Low, 不過這樣會浪費掉一隻16V8的腳,所以在線路圖《圖五》上我們改以將兩個LED A經330 ohm電阻直接接地。另外仔細分析表二發現LED C與LED F的變化是一模一樣,因此只要將LED C 與LED F接在一起即可,因此從16V8輸出的LED C腳又省掉了。就是因為省掉了LED A和 LED C這兩隻腳,最後才使得以一顆16V8設計成功﹝後述﹞。

其餘各組就按LED B的方式寫成布林代數式,以下是給ABEL轉譯程式用的布林代數式,不過有些語法和符號不盡相同,但是各位讀者仔細看一定看的懂。其中有lp0, lp1兩個輸出是給LED F, G, H用的Internal Loop back, 先前提到,16V8做為組合邏輯時,每一個輸出最多可以有7個OR term, 但是LED F, G均超出7個OR term, 因此找出F, G, H的共同項,做成獨立的兩個輸出即lp0, lp1, 然後利用16V8的Internal Loop back功能將之接回LED F, G, H而成為其中一個term。注意,lp0或lp1的所有OR term 迴授到LED F, G, H只成為這些輸出的一個OR term,因此Internal Loop back有擴展OR term的功能。

前面說由於省掉了LED A和 LED C這兩隻腳,最後才使得以一顆16V8設計成功,就是因為化簡到最後發現還要多出lp0, lp1這兩個輸出,結果還好LED A和 LED C這兩隻腳省掉了,剛好用在lp0, lp1上,否則就要用兩顆16V8來完成了。

title '8412 8414 display'

V3DISP device 'P16V8c';

"Input pin definition:"

F2, F1, F0 pin 2,3,4 ; "Freq data"

SEL pin 6; "!8412 / 8141"

CLK pin 7; "H/L word clock"

"Output pin definition"

b pin 19 ; "Light out B"

d pin 18 ; "Light out C"

e pin 17 ; "Light out D"

f pin 16 ; "Light out E"

g pin 15 ; "Light out G"

lp0 pin 14 ; "Internal Loop back"

lp1 pin 13 ; "Internal Loop back"

h pin 12 ; "Light out H"

F = [F2, F1, F0];

equations

b = !SEL & !CLK & (F==3) #!SEL & !CLK & (F==7) #

!SEL & CLK & (F==3) #

!SEL & CLK & (F==7) #

SEL & !CLK & (F==7) #

SEL & CLK & (F==7) ;

d = !SEL & !CLK & (F==0) #!SEL & CLK & (F==0) #

SEL & !CLK & (F==0) #

SEL & !CLK & (F==3) #

SEL & CLK & (F==0) ;

e = !SEL & !CLK & (F==0) #

!SEL & !CLK & (F==3) #

!SEL & !CLK & (F==7) #

!SEL & CLK & (F==0) #

SEL & !CLK & (F==0) #

SEL & !CLK & (F==7) #

SEL & CLK & (F==0) ;

f = !SEL & CLK & (F==3) #!SEL & CLK & (F==7) #

SEL & CLK & (F==3) #

SEL & CLK & (F==7) #

!lp0 # !lp1;

!lp0 = !SEL & !CLK & (F==0) #!SEL & !CLK & (F==1) #

!SEL & !CLK & (F==3) #

SEL & !CLK & (F==3) #

SEL & !CLK & (F==4) #

SEL & !CLK & (F==5) #

SEL & !CLK & (F==7) ;

!lp1= !SEL & !CLK & (F==4) #

!SEL & !CLK & (F==7) #

!SEL & CLK & (F==0) #

SEL & !CLK & (F==0) #

SEL & CLK & (F==0) #

SEL & CLK & (F==4) ;

!g = !lp0 # !lp1;

!h = !SEL & !CLK & (F==2) #

!lp0;

end control

===================================================================

以上ABEL語言寫好之後,16V8接腳配置變成如上圖,將此文字檔輸入電腦,沒兩秒電腦就把我們寫的布林代數式轉為16V8的Fuse Map檔 “xxxxx.jed”,這個檔案就是給燒錄器用的燒錄檔,燒錄方法和EPROM或Flash沒什麼不同,在此不再詳述。

線路圖

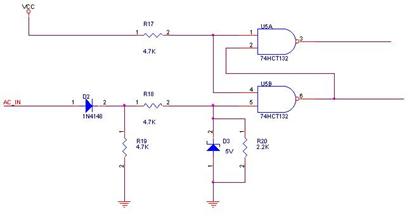

PAL Equation 設計好了,架構也有了,接下來當然要把線路圖畫出來,《圖五》就是完整線路圖, 各位仔細看不難發現與方塊圖架構幾乎一樣,其中U5A與U5B就是Clock反相電路,而Clock Source從何而來呢?如果為此而多加一組Clock產生線路,那未免太浪費了。這個Clock無需太高頻率,其實60Hz就夠了,所以想到三國演義孔明借東風的典型故,主意打到AC Power上。因此利用了DAC的OP Amplifier ±15V在整流濾波之前的AC電源,亦即從變壓器拉一條線到《圖五》的AC_IN, 然後經過D3, R18形成一個波形整流電路,, 再經過D3, 5V齊納二極體形成一個0 ~ 5V的截波整型電路,再送入U5,U5會再做一次波形整型,所以送到PAL 16V8和74LS273時已經是很漂亮的方波了。

整個Design到此告一段落,接下來要付諸行動──裝機。由於一時偷懶不想洗板子,採以萬用板拉線,結果線太多竟然花了更多的工。不過,有志竟成終於完工,接下來通電試機。

PAL Equation 設計好了,架構也有了,接下來當然要把線路圖畫出來,《圖五》就是完整線路圖, 各位仔細看不難發現與方塊圖架構幾乎一樣,其中U5A與U5B就是Clock反相電路,而Clock Source從何而來呢?如果為此而多加一組Clock產生線路,那未免太浪費了。這個Clock無需太高頻率,其實60Hz就夠了,所以想到三國演義孔明借東風的典型故,主意打到AC Power上。因此利用了DAC的OP Amplifier ±15V在整流濾波之前的AC電源,亦即從變壓器拉一條線到《圖五》的AC_IN, 然後經過D3, R18形成一個波形整流電路,, 再經過D3, 5V齊納二極體形成一個0 ~ 5V的截波整型電路,再送入U5,U5會再做一次波形整型,所以送到PAL 16V8和74LS273時已經是很漂亮的方波了。

整個Design到此告一段落,接下來要付諸行動──裝機。由於一時偷懶不想洗板子,採以萬用板拉線,結果線太多竟然花了更多的工。不過,有志竟成終於完工,接下來通電試機。

圖五

圖六 顯示板完成實體

通電之前先將板子上F2, F1, F0這三隻腳以電阻串接三個Jumper,用這三個Jumper來手動設定F2, F1, F0之Hi, Low狀態,加上8412/8414的Jumper就可以驗證顯示的數字是否如我們所期望。

先將F2, F1, F0設定為”000”及8412/8414的Jumper設定為”0”, 我們預期會顯示”EE”外加LED H會亮。很意外的,電一通上,顯示器竟然出現亂碼,再三檢查PAL Equation沒有發現錯誤,最後以示波器測量,發現Clock跟本沒有到達PAL 16V8及74LS273。再往前查,終於找到AC_IN的18V交流電壓經D2, R18到5V齊納二極體截波電路,原本希望AC 18V ( ±25.5Vp) 會被截成0 ~ 5V近似方波,結果波峰是在5V沒錯,但是波谷卻到達不了0 V﹝將近2V﹞,所以U5B的輸入一直沒辦法得到Low的狀態。各位想到是什麼原因了嗎?原來齊納二極體D3的極間電容,讓D2, R18, D3形成一組整流濾波電路,加上U5的輸入阻抗極高,使得D3的極間電容電荷無法宣洩造成波形無法低至0 V。解決方法很簡單,只要讓存在D3的極間電容電荷有地方放電即可,圖七加了兩個電阻R19, R20問題即解決。於是將臨時搭的Jumper調成各種狀態看看是否顯示正確,結果如我們所預期般 ── 一切正常!真沒想到整塊板子最後竟失誤在只有幾個零件的波形整型電路這個最簡單的地方。

呼 ~~!終於可以鬆一口氣,把臨時搭的Jumper拆掉,正式接上DAC。當DAC 一Power On,立即顯示”EE”,CD Player一開就跳成 ”44”,多麼別緻的DAC啊!收拾一下工作桌,一切辛苦終於有了成果,可以好好欣賞音樂了。

圖七 修正後的線路

更發燒的作法

本來,這個製作到此結束了,但是MBL 1611 DAC以兩顆8412分別做為接收轉盤信號與單獨顯示用,他們認為這樣可以防止互相調制干擾,這不正中本製作之要害了嗎?以MBL這種發燒的作法,其實一般發燒型的DIYer應該也可以做到,只是大部分的DIYer都是買PCB來銲的,如果加上額外的8412/8414不僅費錢費工,而且缺乏整體設計的系統恐怕造成機箱內滿肚子的電線,音質可能未受其利先受其害。

想想,如果6.144MHz的clock真會使音質變差,最簡單的方式就是拿掉6.144MHz clock嘛!本顯示器只要加個小電路就可以做到既可顯示頻率又不需要6.144MHz clock!怎麼做呢?我的想法是利用LOCK信號來做控制信號,其思考方向是:

1. LOCK燈的邏輯是:LOCK燈熄掉時一定沒有音樂;有音樂時一定亮著。

2. 沒有音樂時有6.144MHz的clock不影響音質,有音樂時才影響音質。

3. 顯示器早在LOCK燈亮起之前就已顯示正確頻率。

4. 所以讓LOCK燈亮起之前做為顯示器抓取頻率之時期,燈亮起之後將6.144MHz的clock關掉。

5. 顯示器本身有兩個74LS273 D type flip-flop可以儲存顯示資料,只要在6.144MHz的clock關掉的同時﹝或之前﹞將60Hz的clock亦關掉,顯示資料就不會再變動。

6. 這樣,當音樂響起就可以享受沒有干擾的純淨音樂了。

這個構想還沒實現,因為我試過將6.144MHz的clock拿掉與加上,聲音改變實在很小,遠小於換信號線,加上我很累了,所以以後再說啦!這就當成大家一起努力的Home Work吧!

沒有留言:

張貼留言